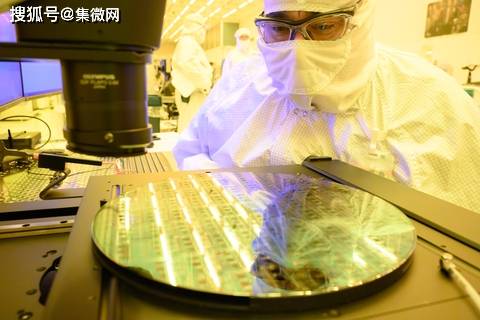

半导体产业长久以来依赖平面缩小技术来提升性能,但这一方法正逐渐逼近物理极限。面对人工智能应用需求的迅猛增长,英特尔、台积电和三星等半导体巨头正加速研发创新解决方案,以期满足下一代计算设备的需求。其中,3D IC技术已成为这些大厂战略布局的关键一环。

近年来,AI大模型的兴起为3D IC技术的快速发展提供了前所未有的契机。3D IC通过垂直堆叠芯片并利用硅通孔(TSV)技术,实现了电子元件的高密度三维集成,与2.5D封装、Chiplet、扇出型封装等先进封装技术一道,成为后摩尔时代提升芯片性能的重要手段。相较于其他技术,3D IC更侧重于高性能计算场景,而其他技术则更注重灵活性与成本效益的平衡。

各大半导体厂商早已涉足3D IC技术的研发,但AI大模型的蓬勃发展无疑为这一领域注入了新的活力。台积电高级副总裁张晓强指出:“为了为客户提供完整的产品级解决方案,晶体管技术和先进封装集成必须并行发展。3D架构技术组合对我们来说已变得至关重要。”

英特尔代工业务的高级副总裁Kevin O’Buckley同样强调了3D IC技术的重要性:“随着内核数量的增加和计算性能的不断提升,满足数据处理需求成为首要任务。3D技术就是一个很好的例子,我们可以利用芯片面积的大部分来放置SRAM,而不必牺牲用于计算的芯片面积。”

尽管3D IC技术显著缩短了元件间的物理距离,提高了芯片性能并降低了功耗,但这一方法也带来了更为复杂的子系统需求,在制造工艺、材料科学和设计方法上都提出了新的挑战。TSV作为3D堆叠的关键技术之一,其工艺直接影响互连密度与良率,需要不断突破更高的深宽比极限。

在制造工艺方面,更先进的等离子刻蚀技术不断涌现,能够实现更高的深宽比和更精确的孔形状控制。在材料方面,除了传统的铜材料外,新的低电阻、高可靠性导电材料如合金材料和碳纳米管复合材料等正在研发中,有望进一步降低信号传输损耗。芯片对芯片键合技术也至关重要,当前的研究重点集中在提高键合精度、速度与可靠性上。

台积电在3D IC领域形成了以SoIC为核心的技术体系,结合CoWoS和硅光子技术,覆盖了从逻辑堆叠到异构集成的全链条。作为SoIC的首发客户,AMD通过SoIC与CoWoS结合,实现了带宽超过5TB/s的AI芯片。台积电正在开发SoIC 2.0技术,目标将互连节距从当前的9μm缩小至5μm,并引入背面供电技术以提升电源效率和散热能力。

英特尔则以Foveros为核心技术,结合EMIB和PowerVia技术,形成了覆盖逻辑堆叠到异构集成的完整技术体系。Foveros通过混合键合和TSV技术实现芯片垂直堆叠,支持高密度集成。英特尔正开发Foveros 2.0技术,目标同样是将互连节距缩小至5μm,并引入背面供电技术。英特尔还在积极开发光连接技术以增强3D IC产品的性能。

三星则以X-Cube为核心技术,在3D IC领域实现了从逻辑堆叠到异构集成的覆盖。X-Cube通过硅通孔和混合键合技术实现芯片垂直堆叠。在热管理技术方面,三星正在开发微流体冷却技术,通过在芯片内部嵌入微米级冷却通道,将散热效率较传统风冷提升3倍。三星还在开发光学I/O技术,并计划将3D IC与下一代制程技术结合,以实现更好的协同效果。